特性摘要

以下為 PECVD DLC 薄膜常見特性區間(以實際需求與規格協作為準)。

| 膜層厚度 | 1 μm ~ 50 μm |

|---|---|

| Sp³ 鍵比率(%) | 50 ~ 70% |

| DLC 膜層硬度(GPa) | 8 ~ 20+(依照應用可進行調整) 比較:SUS 304:<1;Inconel 718/鎳鐵合金:<3;Chrome on Steel/鉻鋼:<10 |

| 磨耗率(mm³/N·m) | 5.1 × 10-7(dry) 比較:SUS 304:1.0 × 10-3;Inconel 718/鎳鐵合金:6.0 × 10-4;Chrome on Steel/鉻鋼:3.0 × 10-4 |

| 乾式摩擦係數(CoF) | < 0.1(dry) |

| 附著力(牛頓力 N) | > 30N |

| 阻抗(Ω) | 1.0 × 109 ~ 1.0 × 1012 |

| 阻抗(Ω) ANSI ESD S2020:2021 | 1.0 × 106 ~ 1.0 × 109 |

| 製程溫度 | 200°C ~ 300°C |

| 膜層耐溫 | 400°C ~ 500°C |

| 抗化學/腐蝕性 | 極佳 |

磨耗率:mm³/N·m =(磨耗體積 mm³)/(載重 N × 磨耗軌跡長度 m);示例條件:25N load per ASTM standard G133-02。

產品圖片

以下為 PECVD DLC 鍍膜之對比與部件展示(示例)。

未鍍膜 vs 鍍膜(對比)

螺桿 & 螺帽:DLC 膜層 4~6 μm

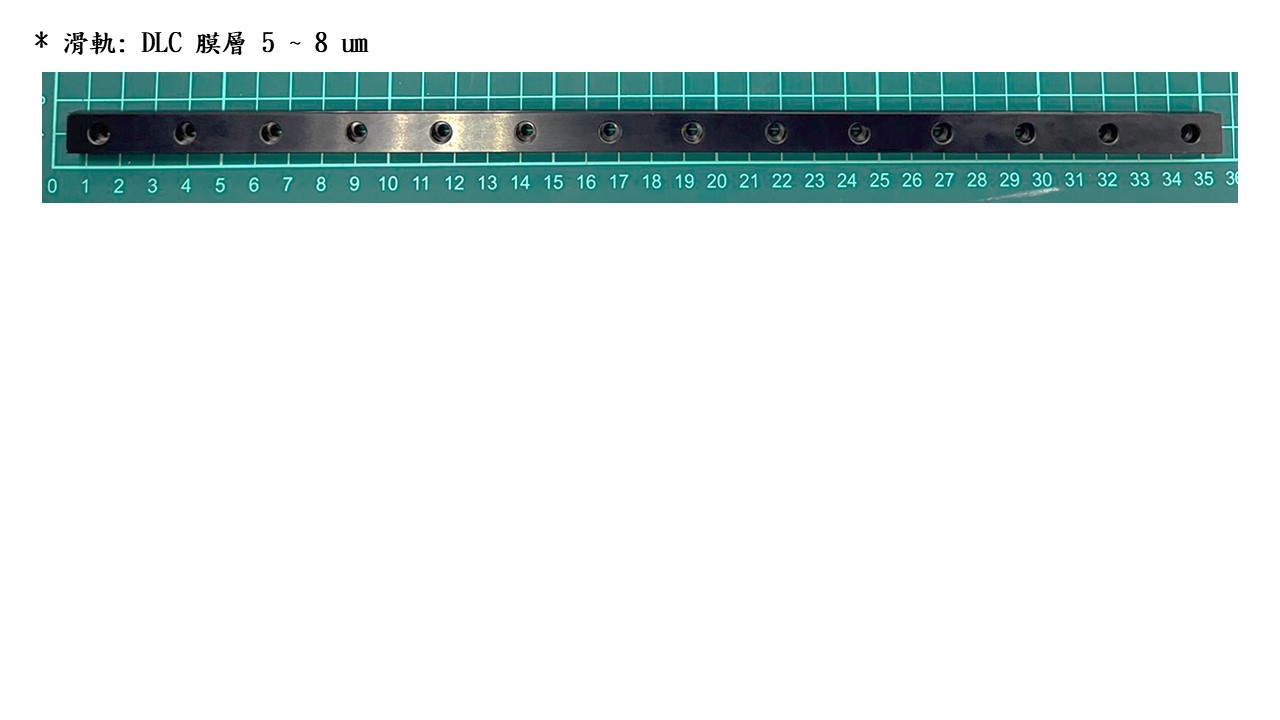

滑軌:DLC 膜層 5~8 μm

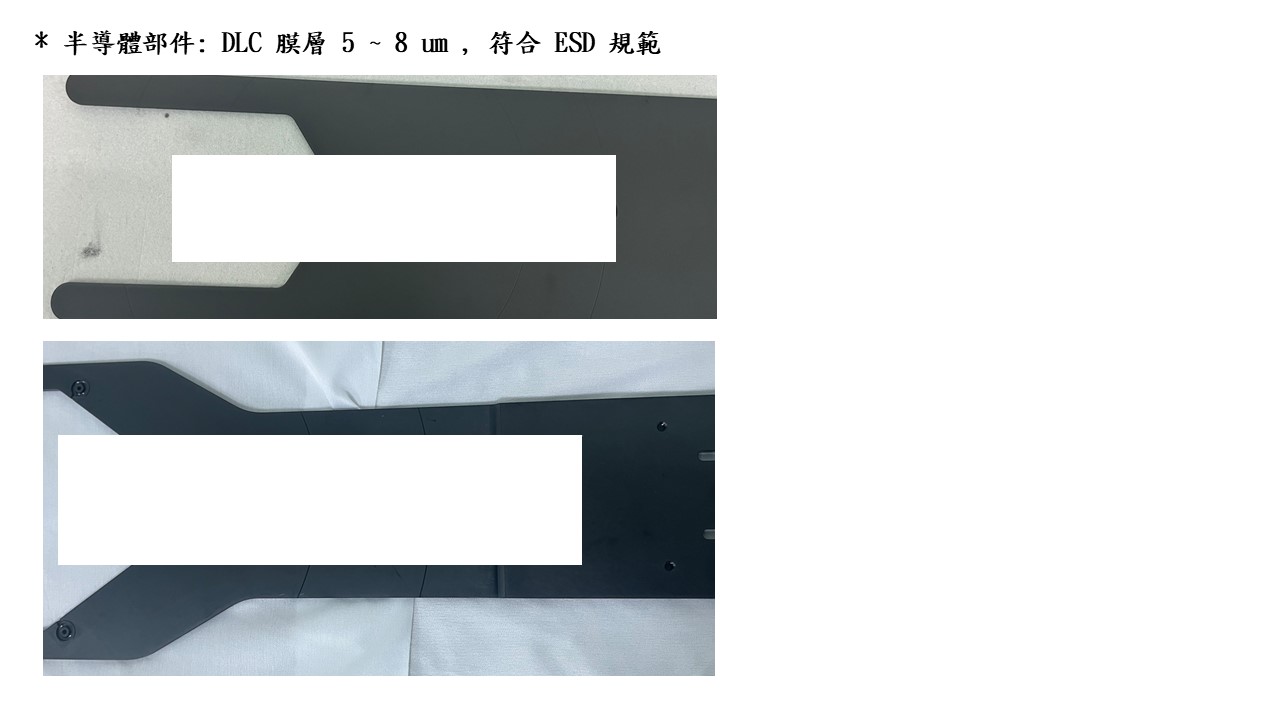

半導體部件:DLC 膜層 5~8 μm,符合 ESD 規範

半導體部件:DLC 膜層 5~8 μm,符合 ESD 規範

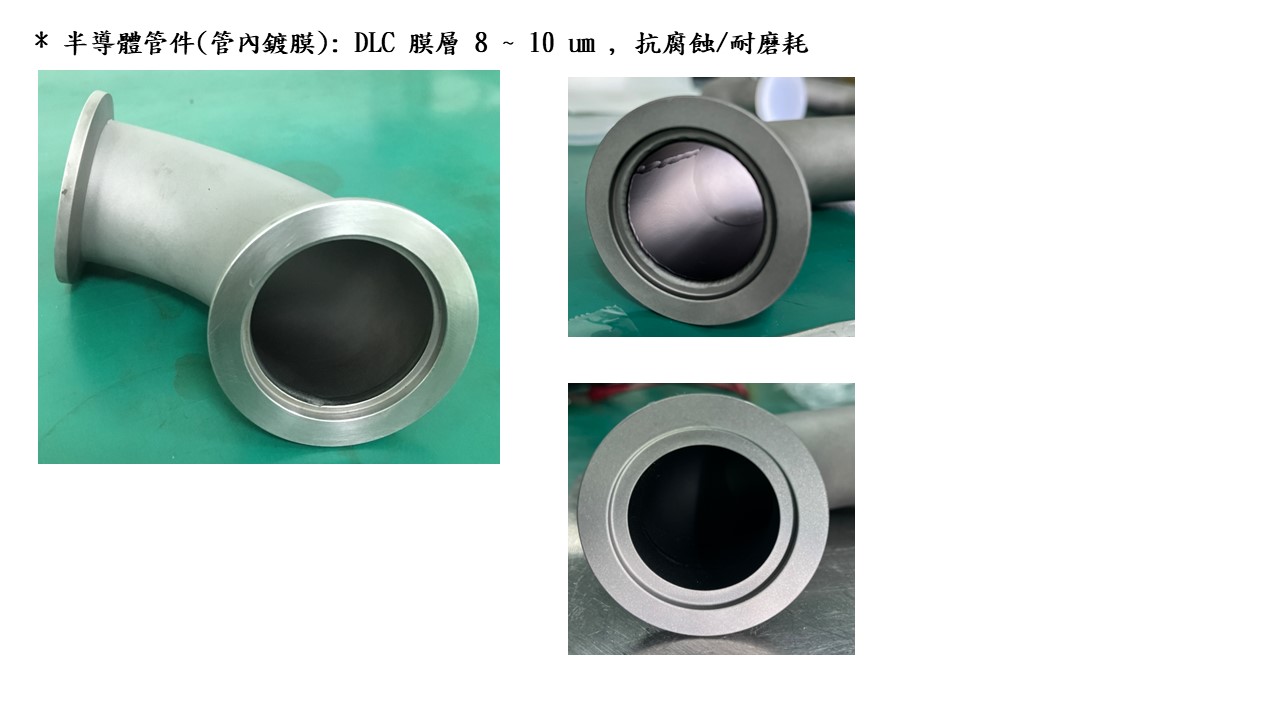

半導體管件(管內鍍膜):DLC 膜層 8~10 μm,抗腐蝕/耐磨耗